搜索到

4

篇与

的结果

-

加快Vivado的编译速度 一. 设置当前Vivado软件使用的线程数,重启软件后失效在Tcl Console中输入命令,如下图。set_param general.maxThreads 32表示设置最大线程数为32。线程数的有效值为1~32。另一个命令:get_param general.maxThreads表示返回当前软件使用的线程数,可用来验证设置线程数是否成功。此方法只在当前Vivado进程中有效,重启软件需要再次设置。二. 设置Vivado默认线程数,重启软件依然生效在Vivado安装路径的scripts文件夹中新建Vivado_init.tcl,名称不能错,Vivado启动时会自动加载此tcl,可以将需要启动执行的命令都写到此tcl文件中。这里在tcl中写入:set_param general.maxThreads 32重启Vivado验证一下,如下图,可见设置默认线程数为32成功。

加快Vivado的编译速度 一. 设置当前Vivado软件使用的线程数,重启软件后失效在Tcl Console中输入命令,如下图。set_param general.maxThreads 32表示设置最大线程数为32。线程数的有效值为1~32。另一个命令:get_param general.maxThreads表示返回当前软件使用的线程数,可用来验证设置线程数是否成功。此方法只在当前Vivado进程中有效,重启软件需要再次设置。二. 设置Vivado默认线程数,重启软件依然生效在Vivado安装路径的scripts文件夹中新建Vivado_init.tcl,名称不能错,Vivado启动时会自动加载此tcl,可以将需要启动执行的命令都写到此tcl文件中。这里在tcl中写入:set_param general.maxThreads 32重启Vivado验证一下,如下图,可见设置默认线程数为32成功。 -

zynq调试网口所遇到的问题记录 1、显示连接正常,出了IP和端口,但tcp client连不上。-----lwIP TCP echo server ------ TCP packets sent to port 6001 will be echoed back link speed for phy address 0: 1000 DHCP Timeout Configuring default IP of 192.168.1.10 Board IP: 192.168.1.10 Netmask : 255.255.255.0 Gateway : 192.168.1.1 TCP echo server started @ port 7解决方法:bank电压设置不对,电压要设置为1.8V2、网络速率协商失败。Start PHY autonegotiation Waiting for PHY to complete autonegotiation. autonegotiation complete Phy setup error Assert due to phy setup failure解决方法:手动设置速率3、网络一直循环连接和断开Link speed for phy address 0: 1000 Ethernet Link up Ethernet Link down Link speed for phy address 0: 1000 Ethernet Link up Ethernet Link down解决方法:此为自带demo的bug,屏蔽掉platform_zynq.c以下代码。/* For detecting Ethernet phy link status periodically */ //if (DetectEthLinkStatus == ETH_LINK_DETECT_INTERVAL) { //eth_link_detect(echo_netif); //DetectEthLinkStatus = 0; //}

zynq调试网口所遇到的问题记录 1、显示连接正常,出了IP和端口,但tcp client连不上。-----lwIP TCP echo server ------ TCP packets sent to port 6001 will be echoed back link speed for phy address 0: 1000 DHCP Timeout Configuring default IP of 192.168.1.10 Board IP: 192.168.1.10 Netmask : 255.255.255.0 Gateway : 192.168.1.1 TCP echo server started @ port 7解决方法:bank电压设置不对,电压要设置为1.8V2、网络速率协商失败。Start PHY autonegotiation Waiting for PHY to complete autonegotiation. autonegotiation complete Phy setup error Assert due to phy setup failure解决方法:手动设置速率3、网络一直循环连接和断开Link speed for phy address 0: 1000 Ethernet Link up Ethernet Link down Link speed for phy address 0: 1000 Ethernet Link up Ethernet Link down解决方法:此为自带demo的bug,屏蔽掉platform_zynq.c以下代码。/* For detecting Ethernet phy link status periodically */ //if (DetectEthLinkStatus == ETH_LINK_DETECT_INTERVAL) { //eth_link_detect(echo_netif); //DetectEthLinkStatus = 0; //} -

Verilog中为inout类型赋值 inout类型的作用inout 类型常出现于芯片外部引脚,为的是减少管腿个数,一个端口同时做输入和输出。inout类型的用法那么,如何判断这个数据段代表输入还是输出呢?一般我们还需要另一个读写控制信号we,根据这个决定inout类型的数据段按读还是写解析。因为inout类型既是input又是output类型,所以必须同时遵守输入输出的描述规定。这个规定也很好理解。因为硬件描述语言的=不是C语言的“覆盖”,而是用一根线将电路中的两个点链接起来。如果这个=表示的电线链接了两个寄存器类型,那么当其中一个reg改变时,另一个无法改变,则会产生冲突。所以用语法规定,盛装某电路模块输出信息的必须是wire类型。那么,在向inout类型传入数据时(tb模块),必须遵守output的规定,使用线网型。(inout接口的另一端必须是wire)

Verilog中为inout类型赋值 inout类型的作用inout 类型常出现于芯片外部引脚,为的是减少管腿个数,一个端口同时做输入和输出。inout类型的用法那么,如何判断这个数据段代表输入还是输出呢?一般我们还需要另一个读写控制信号we,根据这个决定inout类型的数据段按读还是写解析。因为inout类型既是input又是output类型,所以必须同时遵守输入输出的描述规定。这个规定也很好理解。因为硬件描述语言的=不是C语言的“覆盖”,而是用一根线将电路中的两个点链接起来。如果这个=表示的电线链接了两个寄存器类型,那么当其中一个reg改变时,另一个无法改变,则会产生冲突。所以用语法规定,盛装某电路模块输出信息的必须是wire类型。那么,在向inout类型传入数据时(tb模块),必须遵守output的规定,使用线网型。(inout接口的另一端必须是wire) -

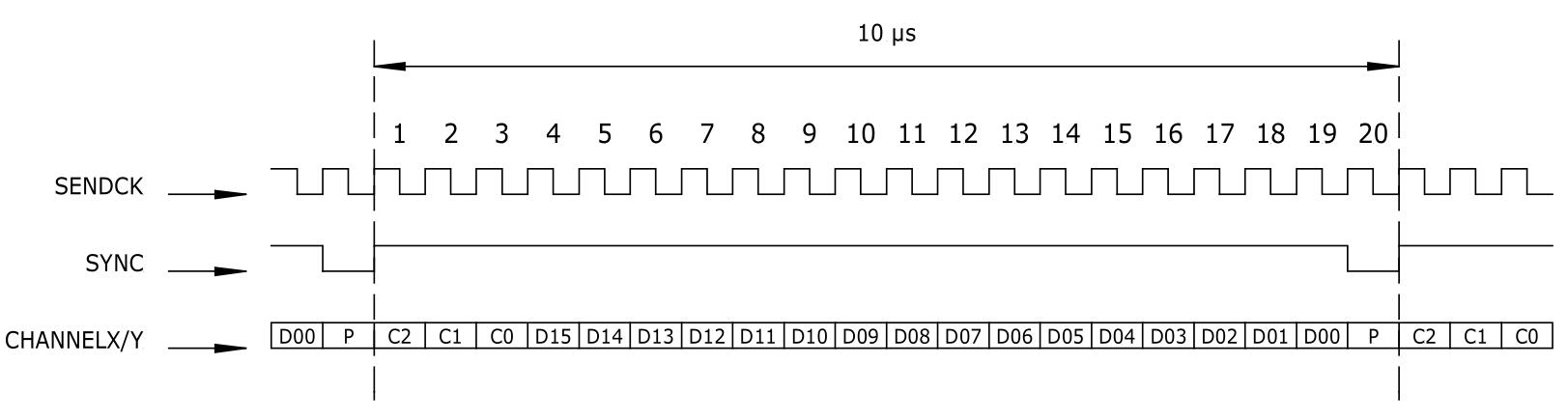

数字振镜XY2-100协议 一、协议格式该协议时钟(SENDCK)为2MHz ,SYNC为同步信号,CHANNELX/Y 是数据信号,它有20位组成,其中C2、C1、C0是振镜运动方向值,参考值为001,D15—D0是数据位,它是16位的二进制数,用来控制振镜转过的角度大小(取值为0~65535,即将振镜轴的转动角度范围映射到0~65535);最后一位是偶校验位,当发送的数 据中有偶数个“1”时,对应的校验位为“0”。当发送的数据中有奇数个“1”时对应的校验位为“1”。二、FPGA(Verilog)代码实现module xy2_100( //端口列表 rst_n, clk50m, send_en, x_data, y_data, sendck, sync, chl_x, chl_y, TxDone, xy2_state ); //端口定义 input rst_n; input clk50m; input send_en; input [15:0]x_data; input [15:0]y_data; output reg sendck; output reg sync; output reg chl_x; output reg chl_y; output reg TxDone; output reg xy2_state; reg [4:0]div_cnt;//分频计数器 reg [4:0]bps_cnt;//波特率时钟计数器 reg [15:0]r_data_x; reg [15:0]r_data_y; localparam bps_DR = 5'd24; //分频计数最大值 localparam CTRL_WD = 3'b001; //控制字 localparam MAX_BIT = 5'd20; //发送状态信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) xy2_state <= 1'b0; else if(send_en) xy2_state <= 1'b1; else if(bps_cnt == MAX_BIT) xy2_state <= 1'b0; else xy2_state <= xy2_state; //发送数据锁存 always@(posedge clk50m or negedge rst_n) if(!rst_n) r_data_x <= 15'd0; else if(send_en) r_data_x <= x_data; else r_data_x <= r_data_x; always@(posedge clk50m or negedge rst_n) if(!rst_n) r_data_y <= 15'd0; else if(send_en) r_data_y <= y_data; else r_data_y <= r_data_y; //分频计数器 always@(posedge clk50m or negedge rst_n) if(!rst_n) div_cnt <= 5'd0; else if(xy2_state||send_en) begin if(div_cnt == bps_DR) div_cnt <= 5'd0; else div_cnt <= div_cnt+1'b1; end else div_cnt <= 5'd0; // bps counter always@(posedge clk50m or negedge rst_n) if(!rst_n) bps_cnt <= 5'd0; else if(bps_cnt==MAX_BIT) bps_cnt <= 5'd0; else if(div_cnt==bps_DR) bps_cnt <= bps_cnt + 1'b1; else bps_cnt <= bps_cnt; // 发送完成信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) TxDone <= 1'b0; else if(bps_cnt == MAX_BIT) TxDone <= 1'b1; else TxDone <= 1'b0; // x按位发送数据 always@(posedge clk50m or negedge rst_n) if(!rst_n) chl_x <= 1'b0; else if(div_cnt==5'd0) begin case (bps_cnt) 0:chl_x <= 1'b0; //c2 1:chl_x <= 1'b0; //c1 2:chl_x <= 1'b1; //c0 3:chl_x <= r_data_x[15]; 4:chl_x <= r_data_x[14]; 5:chl_x <= r_data_x[13]; 6:chl_x <= r_data_x[12]; 7:chl_x <= r_data_x[11]; 8:chl_x <= r_data_x[10]; 9:chl_x <= r_data_x[9]; 10:chl_x <= r_data_x[8]; 11:chl_x <= r_data_x[7]; 12:chl_x <= r_data_x[6]; 13:chl_x <= r_data_x[5]; 14:chl_x <= r_data_x[4]; 15:chl_x <= r_data_x[3]; 16:chl_x <= r_data_x[2]; 17:chl_x <= r_data_x[1]; 18:chl_x <= r_data_x[0]; 19:chl_x <= ^{CTRL_WD,r_data_x}; //偶校验 default:chl_x <= 1'b0; endcase end // y按位发送数据 always@(posedge clk50m or negedge rst_n) if(!rst_n) chl_y <= 1'b0; else if(div_cnt==5'd0) begin case (bps_cnt) 0:chl_y <= 1'b0; //c2 1:chl_y <= 1'b0; //c1 2:chl_y <= 1'b1; //c0 3:chl_y <= r_data_y[15]; 4:chl_y <= r_data_y[14]; 5:chl_y <= r_data_y[13]; 6:chl_y <= r_data_y[12]; 7:chl_y <= r_data_y[11]; 8:chl_y <= r_data_y[10]; 9:chl_y <= r_data_y[9]; 10:chl_y <= r_data_y[8]; 11:chl_y <= r_data_y[7]; 12:chl_y <= r_data_y[6]; 13:chl_y <= r_data_y[5]; 14:chl_y <= r_data_y[4]; 15:chl_y <= r_data_y[3]; 16:chl_y <= r_data_y[2]; 17:chl_y <= r_data_y[1]; 18:chl_y <= r_data_y[0]; 19:chl_y <= ^{CTRL_WD,r_data_y}; //偶校验 default:chl_y <= 1'b0; endcase end //同步信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) sync <= 1'b0; else if(send_en) sync <= 1'b1; else if(bps_cnt==(MAX_BIT-1)) //&&(div_cnt==5'd0)) sync <= 1'b0; else sync <= sync; //发送时钟信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) sendck <= 1'b0; else if((xy2_state||send_en)&&(bps_cnt<MAX_BIT)) begin if(div_cnt<=bps_DR/2) sendck <= 1'b1; else sendck <= 1'b0; end else sendck <= 1'b0; endmodule

数字振镜XY2-100协议 一、协议格式该协议时钟(SENDCK)为2MHz ,SYNC为同步信号,CHANNELX/Y 是数据信号,它有20位组成,其中C2、C1、C0是振镜运动方向值,参考值为001,D15—D0是数据位,它是16位的二进制数,用来控制振镜转过的角度大小(取值为0~65535,即将振镜轴的转动角度范围映射到0~65535);最后一位是偶校验位,当发送的数 据中有偶数个“1”时,对应的校验位为“0”。当发送的数据中有奇数个“1”时对应的校验位为“1”。二、FPGA(Verilog)代码实现module xy2_100( //端口列表 rst_n, clk50m, send_en, x_data, y_data, sendck, sync, chl_x, chl_y, TxDone, xy2_state ); //端口定义 input rst_n; input clk50m; input send_en; input [15:0]x_data; input [15:0]y_data; output reg sendck; output reg sync; output reg chl_x; output reg chl_y; output reg TxDone; output reg xy2_state; reg [4:0]div_cnt;//分频计数器 reg [4:0]bps_cnt;//波特率时钟计数器 reg [15:0]r_data_x; reg [15:0]r_data_y; localparam bps_DR = 5'd24; //分频计数最大值 localparam CTRL_WD = 3'b001; //控制字 localparam MAX_BIT = 5'd20; //发送状态信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) xy2_state <= 1'b0; else if(send_en) xy2_state <= 1'b1; else if(bps_cnt == MAX_BIT) xy2_state <= 1'b0; else xy2_state <= xy2_state; //发送数据锁存 always@(posedge clk50m or negedge rst_n) if(!rst_n) r_data_x <= 15'd0; else if(send_en) r_data_x <= x_data; else r_data_x <= r_data_x; always@(posedge clk50m or negedge rst_n) if(!rst_n) r_data_y <= 15'd0; else if(send_en) r_data_y <= y_data; else r_data_y <= r_data_y; //分频计数器 always@(posedge clk50m or negedge rst_n) if(!rst_n) div_cnt <= 5'd0; else if(xy2_state||send_en) begin if(div_cnt == bps_DR) div_cnt <= 5'd0; else div_cnt <= div_cnt+1'b1; end else div_cnt <= 5'd0; // bps counter always@(posedge clk50m or negedge rst_n) if(!rst_n) bps_cnt <= 5'd0; else if(bps_cnt==MAX_BIT) bps_cnt <= 5'd0; else if(div_cnt==bps_DR) bps_cnt <= bps_cnt + 1'b1; else bps_cnt <= bps_cnt; // 发送完成信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) TxDone <= 1'b0; else if(bps_cnt == MAX_BIT) TxDone <= 1'b1; else TxDone <= 1'b0; // x按位发送数据 always@(posedge clk50m or negedge rst_n) if(!rst_n) chl_x <= 1'b0; else if(div_cnt==5'd0) begin case (bps_cnt) 0:chl_x <= 1'b0; //c2 1:chl_x <= 1'b0; //c1 2:chl_x <= 1'b1; //c0 3:chl_x <= r_data_x[15]; 4:chl_x <= r_data_x[14]; 5:chl_x <= r_data_x[13]; 6:chl_x <= r_data_x[12]; 7:chl_x <= r_data_x[11]; 8:chl_x <= r_data_x[10]; 9:chl_x <= r_data_x[9]; 10:chl_x <= r_data_x[8]; 11:chl_x <= r_data_x[7]; 12:chl_x <= r_data_x[6]; 13:chl_x <= r_data_x[5]; 14:chl_x <= r_data_x[4]; 15:chl_x <= r_data_x[3]; 16:chl_x <= r_data_x[2]; 17:chl_x <= r_data_x[1]; 18:chl_x <= r_data_x[0]; 19:chl_x <= ^{CTRL_WD,r_data_x}; //偶校验 default:chl_x <= 1'b0; endcase end // y按位发送数据 always@(posedge clk50m or negedge rst_n) if(!rst_n) chl_y <= 1'b0; else if(div_cnt==5'd0) begin case (bps_cnt) 0:chl_y <= 1'b0; //c2 1:chl_y <= 1'b0; //c1 2:chl_y <= 1'b1; //c0 3:chl_y <= r_data_y[15]; 4:chl_y <= r_data_y[14]; 5:chl_y <= r_data_y[13]; 6:chl_y <= r_data_y[12]; 7:chl_y <= r_data_y[11]; 8:chl_y <= r_data_y[10]; 9:chl_y <= r_data_y[9]; 10:chl_y <= r_data_y[8]; 11:chl_y <= r_data_y[7]; 12:chl_y <= r_data_y[6]; 13:chl_y <= r_data_y[5]; 14:chl_y <= r_data_y[4]; 15:chl_y <= r_data_y[3]; 16:chl_y <= r_data_y[2]; 17:chl_y <= r_data_y[1]; 18:chl_y <= r_data_y[0]; 19:chl_y <= ^{CTRL_WD,r_data_y}; //偶校验 default:chl_y <= 1'b0; endcase end //同步信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) sync <= 1'b0; else if(send_en) sync <= 1'b1; else if(bps_cnt==(MAX_BIT-1)) //&&(div_cnt==5'd0)) sync <= 1'b0; else sync <= sync; //发送时钟信号 always@(posedge clk50m or negedge rst_n) if(!rst_n) sendck <= 1'b0; else if((xy2_state||send_en)&&(bps_cnt<MAX_BIT)) begin if(div_cnt<=bps_DR/2) sendck <= 1'b1; else sendck <= 1'b0; end else sendck <= 1'b0; endmodule